# 3870 SINGLE CHIP MICRO FAMILY MK3870 and MK38P70

#### MK3870 FEATURES

- Available with 1K, 2K, 3K, or 4K bytes of mask programmable ROM memory

- 64 bytes scratchpad RAM

- □ Available with 64 bytes executable RAM

- □ 32 bits (4 ports) TTL compatible I/O

- Programmable binary timer Interval timer mode

Pulse width measurement mode

Event counter mode

- □ External interrupt input

- ☐ Crystal, LC, RC, or external time base options

- ☐ Low power (275 mW typ.)

- ☐ Single +5 volt supply

#### MK38P70 FEATURES

- □ EPROM version of MK3870

- ☐ Piggyback PROM (P-PROM)™ package

- ☐ Accepts 24 pin or 28 pin EPROM memories

- □ Identical pinout as MK3870

- ☐ In-Socket emulation of MK3870

### GENERAL DESCRIPTION

The MK3870 is a completes bit microcomputer on a single MOS integrated circuit. The MK3870 can execute a set of more than 70 instructions, and is completely software compatible with the rest of the devices in the 3870 family. The MK3870 features 1-4K bytes of ROM and optional additional executable RAM depending on the specific part yep designated by a slash number suffix. The MK3870 also features 64 bytes of scratchpad RAM, a programmable binary timer, and 32 bits of 1/0.

The programmable binary timer operates by itself in the interval timer mode or in conjunction with the external interrupt input in the pulse width measurement and the

| MK3870 PIN CONNEC | CTIONS |                        |

|-------------------|--------|------------------------|

| x1(1 → 1 □        |        | □ 40 + V <sub>cc</sub> |

| x71.2 → 2 □       |        | □ 39 → RESET           |

| F00 3 []          |        | ☐ 38 EXT INT           |

| P0 1 4 [          |        | 37 ++ FTG              |

| FO 2 5            |        | 36 ++ Fil              |

| F53 ←→ 6 □        |        | 35 →→ P/2              |

| STROBE - 7        |        | 34 ++ Pl3              |

| P40 8 []          |        | 33 ++ 150              |

| F41 ←→ 9 □        |        | 32 ++ P57              |

| P4 2 10 []        | MK3870 | 31 ++ 55               |

| F43 +++ 11        |        | 30 ++ F53              |

| P4 4 12           |        | 29 ++ 1572             |

| F43 13            |        | 28 ++ 553              |

| P4 6 14           |        | 27 ++ 55.6             |

| F47 ++ 15 [       |        | 26 ++ 553              |

| R57 ↔ 16 [        |        | 25 ++ F17              |

| FG6 ++ 17         |        | 24 ++ FT&              |

| FOS ++ 18         |        | 23 ++ FB               |

| PO 4 19 [         |        | 22 FT4                 |

|                   |        |                        |

#### MK38P70 PIN CONNECTIONS

GND - 201

| XTL1 1      |           | 40 ← V <sub>66</sub> |

|-------------|-----------|----------------------|

| xTL2 → 2 □  |           | 39 ← RESEY           |

| F00 3 []    |           | 38 ← FXT INT         |

| PO 1 4 []   |           | 37 P10               |

| F02 → 5 🗍   | . 28 •    | 36 ++ PIT            |

| F53 ←→ 6 [] | . 3 25 .  | 35 ++ HT             |

| STROBE - 7  |           | 34 73                |

| ALD ←→ 8 □  | •         | 33 ++ 550            |

| F43 ++ 9 [] | •         | 32 ++ 853            |

| F4 2 10     | MK38P70   | 31 ++ 80             |

| FT3 ++ 11   | •         | 30 ++ BC)            |

| F4.4 ++ 12  |           | 29 ++ 554            |

| F4T3 13     | •         | 28 (573              |

| FE 6 14 1   | •         | 27 ++ 653            |

| P4 7 15     |           | 26 ++ B3             |

| FØ7 ◆◆ 16 T | •         | 25 ++ 57             |

| FD 6 ++ 17  | •         | 24 ++ FT             |

| PDS 18 1    | • 14 15 e | 23 573               |

| FO 4 ++ 19  |           | 722 573              |

event counter modes of operation. Two sources of vectored. prioritized interrupt are provided with the binary timer and the external interrupt input. The user has the option of specifying one of four clock sources for the MK3870 and MK38P70: Crystal, LC, RC, or external clock, In addition, the user can specify either a ±10% power supply tolerance or a ±5% power supply tolerance.

The MK38P70 microcomputer is the PROM based version of the MK3870. It is called the piggyback PROM (P-PROM)TM because of its packaging concept. This concept allows a standard 24-pin or 28 pin EPROM to be mounted directly on top of the microcomputer itself. The EPROM can be removed and reprogrammed as required with a standard PROM programmer. The MK38P70 retains exactly the same pinout and architectural features as other members of the 3870 family. The MK38P70 is discussed in more detail in a later section.

| PIN NAME     | DESCRIPTION        | TYPE          |

|--------------|--------------------|---------------|

| PO-0 PO-7    | I/O Port 0         | Bidirectional |

| P1-0 P1-7    | I/O Port 1         | Bidirectional |

| P4-0 P4-7    | I/O Port 4         | Bidirectional |

| P5-0 P5-7    | I/O Port 5         | Bidirectional |

| STROBE       | Ready Strobe       | Output        |

| EXT INT      | External Interrupt | Input         |

| RESET        | External Reset     | Input         |

| TEST         | Test Line          | Input         |

| XTL 1, XTL 2 | Time Base          | Input         |

| VCC, GND     | Power Supply Lines | Input         |

PO-O-- PO-7, P1-O--P1-7, P4-O--P4-7, and P5-O--P5-7 are 32 lines which can be individually used as either TTL compatible inputs or as latched outputs.

STROBE is a ready strobe associated with I/O Port 4. This pin, which is normally high, provides a single low pulse after valid data is present on the P4-0-P4-7 pins during an output instruction.

RESET may be used to externally reset the MK3870. When pulled low the MK3870 will reset. When then allowed to go high the MK3870 will begin program execution at program location H '000'.

EXT INT is the external interrupt input. Its active state is software programmable. This input is also used in conjunction with the timer for pulse width measurement and event counting.

XTL 1 and XTL 2 are the time base inputs to which a crystal, LC network, RC network, or an external single-phase clock may be connected. The time base network must be specified when ordering a mask ROM MK3870. The MK38P70 will operate with any of the four configurations.

TEST is an input, used only in testing the MK3870. For normal circuit function this pin may be left unconnected, but V<sub>CC</sub> is the power supply input (single +5v).

#### MK3870 ARCHITECTURE

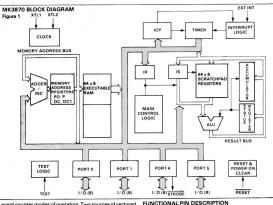

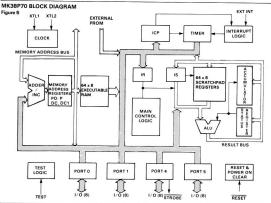

The basic functional elements of the MK3870 are shown in Figure 1. A programming model is shown in Figure 2. The

architecture is common to all members of the 3870 family. All 3870 devices are instruction soft compatible and differ only in amount and type of ROM, RAM, and I/O. The unique features of the MK3870 are discussed in the following sections. The user is referred to the 3870 Family Technical Manual for a thorough discussion of the architecture, instruction set, and other features which are common to all 3870 family devices.

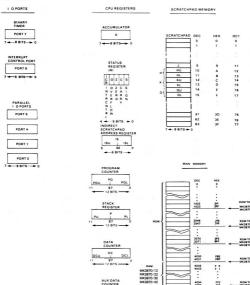

#### MK3870 PROGRAMMABLE REGISTERS, PORTS, AND MEMORY MAP Figure 2

DC1

- 12 BITS

7 -- 8 BITS-- 0

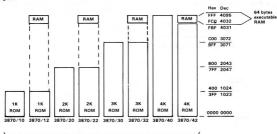

#### MK3870 MAIN MEMORY SIZES AND TYPES BY SLASH NUMBERS Figure 3

All devices contain 64 bytes of scratchpad RAM.

NOTE: Data derived from addressing any locations other than those within a part's specified ROM space or RAM space (if any) are not tested nor are the data guaranteed. Users should refrain from entering this area of the memory map.

| Device     | Scratchpad<br>RAM Size<br>(Decimal) | Address<br>Register Size<br>(P0, P, DC, DC1) | ROM<br>Size<br>(Decimal) | Executable<br>RAM Size |

|------------|-------------------------------------|----------------------------------------------|--------------------------|------------------------|

| MK3870/10  | 64 bytes                            | 12 bits                                      | 1024 bytes               | 0 bytes                |

| MK3870/12  | 64 bytes                            | 12 bits                                      | 1024 bytes               | 64 bytes               |

| MK3870/20* | 64 bytes                            | 12 bits                                      | 2048 bytes               | 0 bytes                |

| MK3870/22  | 64 bytes                            | 12 bits                                      | 2048 bytes               | 64 bytes               |

| MK3870/30  | 64 bytes                            | 12 bits                                      | 3072 bytes               | 0 bytes                |

| MK3870/32  | 64 bytes                            | 12 bits                                      | 3072 bytes               | 64 bytes               |

| MK3870/40  | 64 bytes                            | 12 bits                                      | 4096 bytes               | 0 bytes                |

| MK3870/42  | 64 bytes                            | 12 bits                                      | 4032 bytes               | 64 bytes               |

<sup>\*</sup>The MK3870/20 is equivalent to the original 3870 device in memory size; however, the original 3870 had an 11-bit Address Register. The original 3870 with 11-bit Address Register is available where required. Consult the section describing ROM Code Ordering Information for additional information.

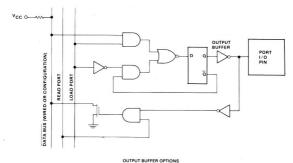

#### I/O PIN CONCEPTUAL DIAGRAM WITH OUTPUT BUFFER OPTIONS Figure 4

Ports 0 and 1 are Standard Output type only.

Ports 4 and 5 may both be any of the three output options (mask programmable bit by bit)

The STROBE output is always configured similar to a Direct Drive Output except that it is capable of driving 3 TTL loads.

RESET and EXT INT may have standard 6K() (typical) pull-up or may have no pull-up (mask programmable).

RESET and EXT INT do not have internal pull up on the MK38P70.

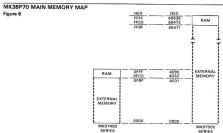

#### MK3870 MAIN MEMORY

There are four address registers used to access main memory. These are the Program Counter (PO), the State Register (P), the Data Counter (DC), the Auxiliary Data Counter (DC), the Program Counter (DC), and the Auxiliary Data Counter (DC). The Program Counter (DCI) are the State Register instructions or immediate operands. The Stack Register instructions or immediate operands. The Stack Register contains the return address at which processing interrupt or subroutine call. Thus, the Stack Register contains the return address at which processing contains the return address at which processing the Counter is used to address data that Counter is used to address data that Counter is used to address data that Counter is one Counters, only Data Counter (DC), can access the RDM. However, the XDC instruction allows the Data Counter and Auxiliary Data Counter to be exclusive to the State Counter and Auxiliary Data Counter to be exclusive to the State Counter and Auxiliary Data Counter to the exclusive the State Counter and Auxiliary Data Counter to the exclusive the State Counter and Auxiliary Data Counter to the exclusive the State Counter and Auxiliary Data Counter to the exchanged.

The graph in Figure 3 shows the amounts of ROM and executable RAM for every available slash number in the MK3870 pin configuration.

#### EXECUTABLE RAM

The upper bytes of the address space in some of the MK3870 devices are RAM memory. As with the ROM memory, the RAM may be addressed by the P0 and the DC address registers. The executable RAM may be addressed by all MK3870 instructions which address Main Memory. Additionally, the MK3870 my execute an instruction sequence which resides in the executable RAM. Note this cannot be done with the scratchpad RAM memory, which is the reason the term "executable RAM" is given to this additional memory.

#### I/O PORTS

The MK3870 provides four, 8 bit bidirectional Input/Output ports. These are ports 0.1, 4.6. In addition, the Interrupt Control Port is addressed as Port 1.6 and the binary timer is addressed as Port 7. The programming of Ports 6 and 7 and the bidirectional I/O pin are covered in the 3870 Family Technical Manual. The schematic of an I/O pin and available output drive octions are shown in Figure 4.

An output ready strobe is associated with Port 4. This flag may be used to signal a peripheral device that the MKS870 has just completed an output of new data to Port 4. The strobe provides a single low pulse shortly after the output operation is completely finished, so either edge may be used to signal the peripheral. STROBE may also be used as an input strobe to Port 4 after completing the input operation.

#### MK38P70 GENERAL DESCRIPTION

The MK38P70 is the EPROM version of the MK3870. It retains an identical pinout with the MK3870, which is documented in the section of this data sheet entitled "FUNCTIONAL PIN DESCRIPTION". The MK38P70 is housed in two packages which incorporate a 28-pin socket

located directly on top of the package. A number of standard EPROMs may be plugged into this socket.

The MK38P70 can act as an emulator for the purpose of verification of user code prior to the ordering of mask ROM MK3870 devices. Thus, the MK38P70 eliminates the need for emulator board products. In addition, several MK38P70 act can be used in prototype systems in order to test design concepts in field service before committing to high-volume production with mask ROM MK3870s. The compact size of the MK38P70 EPROM combination allows the packaging of such prototype systems to be the same as that used in production. Finally, in low-volume applications, the MK38P70 can be used as the actual production device.

Most of the material which has been presented for the MK3870 in this document applies to the MK38P0 his includes the description of the pin configuration, architecture, programming model, and I/O ports. Additional information is presented in the following sections.

#### MK38P70 MAIN MEMORY

There are two basic versions of the MK38P70. These are the 97400 series and the 97500 series. The 97400 series parts have twelve bit address capability thus a total 4K memory map like the MK3870 ROM devices. The 97500 series has 16 bit address canability.

As can be seen from Figure 6, both the 97400 series and the 97500 series contain on-chip RAM in the upper portion of their memory maps and no on-chip ROM. Instead of on-chip ROM, address and data lines are brought out to the 28 pin socket located directly on top of the 40 pin package so that external memory devices (principally EPROMs) are addressed

By using an external EPROM, the 38P70 may be used to emulate the 3870 ROM devices. The 97400 series can directly emulate the following devices.

MK3870/10 MK3870/20

MK3870/20

MK3870/30 MK3870/42

The MK3807/40 cannot be emulated exactly by the 97400 series because the 97400 devices have the 64 bytes of RAM in the upper memory map while the 3870/40 provides ROM memory in this address space.

Besides the difference in the size of the address registers, 97500 series can also emulate many of the 3870 ROM devices. This difference in address capability should not cause any functional difference as long as normal programming practice is used. That is, as long as address roll-over or automatic truncation is not used. One such usage would be an end around branch (branching forward

| MK38P70<br>TYPE | SCRATCHPAD<br>RAM SIZE<br>(DECIMAL) | ADDRESS<br>REGISTER<br>SIZE | EXTERNALLY<br>ADDRESSABLE<br>MEMORY<br>SIZE | INTERNAL<br>EXECUTABLE<br>RAM<br>SIZE |

|-----------------|-------------------------------------|-----------------------------|---------------------------------------------|---------------------------------------|

| 97400 Series    | 64 bytes                            | 12 bits                     | 4032 bytes                                  | 64 bytes                              |

| 97500 Series    | 64 bytes                            | 16 bits                     | 65472 bytes                                 | 64 bytes                              |

MK38P70 devices have no internal ROM memory.

at upper memory to get to lower memory). Another case would be in using automatic truncation of data loaded into the 12 bit address registers on the ROM devices. For example, to access some particular location (03FF hex for example) via the data counter, one could load that address into DC using the DCI instruction. The instruction

DCI '73FF'

would cause 3FF to be loaded into the DC of the 3870 ROM device because the upper bits of the DC bits 12-15 ROM not exist. If that instruction was followed by the LM instruction have followed by the LM instruction. He data stored at location 3FF would be obtained to 18-7500 series devices would not truncate the 73FF address on 3FF. As previously stated, this type of programming is generally not done and thus the 97500 devices can be used to emulate the following devices directly.

MK3870/10 MK3870/20

MK3870/30 MK3870/40

The 97500 series can also be used to emulate the remainder of the 3870 devices a long as one accounts for the difference in the location of the RAM memory. In the 97500 devices, RAM is located at FFC0 through FVC0 While in 3870 devices this RAM (when it exists) is located at 0FC0 through OFFF. When this minor difference is accounted for, the 97500 series will also emulate the following devices.

MK3870/22 MK3870/42

#### MK38P70 FPROM SOCKET

A 28 pin socket is located on top of the 40 pin package. When 24 pin memories are used, they are inserted so that pin 1 of the memory device is plugged into pin 3 of the socket (the 24 pin memory is lower justified in the 28 pin socket).

A 24 pin top socket was used so that the same package could be used for all 38P70 devices but could accommodate both 24 pin and 28 pin. Due to pin-out differences between various common memory devices, several different versions of the MK38P70 are provided with differing signals connected to particular pins on the 28 pin socket. Figure 7 shows the various options available.

#### MK38P70 I/O PORTS

For custom 3870 ROM codes, the user is given a bit by bit selection of I/O options on I/O ports 4 and 5. Additionally, the user has the option of selecting whether or not either RESET or EXT INT has an internal pull-up resistor. This idexbility allows about 172 million possible variations in I/O port and RESET and EXT INT configurations. Diviously, it is not practical to offer this variety in an "off the shelf" product like the 38P70. Thus a few variations are offered which still give some flexibility to the designer. The available I/O options are also shown in Figure 7.

#### 28 PIN SOCKET SIGNALS

The 40 package pins are the identical signals that are provided with the MK3870 ROM devices. In addition to these 40 inputs and outputs, various other signals are implemented on the 38P70 die which are available connection to the top socket. Depending upon the particular version, some subset of these signals are connected to the 28 pin socket. These signals are described below.

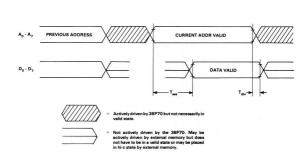

#### A<sub>0</sub> - A<sub>11</sub> (97400 Series) A<sub>0</sub> - A<sub>15</sub> (97500 Series)

These are the address buses. They are always outputs and a new address will appear on this bus during each machine cycle. Normally this is the address of op-codes or operands, but there are machine cycles wherein no op-code or operand is required by the CPU. During these cycles, an address is still provided but the data that may be read from that address is not used.

#### Do - D7 (97400 and 97500 Series)

This is the bi-directional data bus for the external memory. Normally these lines are high impedance inputs. During op-code or operand reads, they receive data from the external memory and conduct it onto the internal 38P70 data bus. During those cycles wherein the operation is strictly internal to the 38P70, they remain hi-z inputs. Data may be presented to the 38P70 by an external memory device but it is not conducted onto the internal data bus. This includes machine cycles wherein op-codes or operands are read from the internal executable RAM. During the operand write machine cycle that occurs in the ST (store) instruction, they become push-pull outputs to conduct data to be written out to the external memory. However, if data is written to the internal executable RAM, this transaction is strictly internal and thus the data bus lines remain in their hi-z state. It, therefore, depends upon the address as to whether this bus becomes an active output bus or remains high impedance. If the address of the operand is not within the internal executable RAM space when a ST instruction is executed, Do - Do will become active outputs at the appropriate time, or else they will remain in the hi-z state. The 97400 devices do not provide a RD (read) control signal, nor is this signal provided on all versions of the 97500 series. Thus if a ST is executed with the operand address being that of external memory, that memory may access data and drive it onto Do - Do while the 38P70 is also driving data onto Do -D7 and a bus conflict will result. This condition should be avoided; thus the user should note whether or not his external memory will drive Do - Do in this event. If it will drive Do - D7, an ST with that operand address should be avoided. In general, one would not normally execute a write to a memory location where there is ROM or EPROM memory instead of RAM. However, some 3870 users have

| DEVICE  | PORT 4<br>I/O TYPE | PORT 5<br>I/O TYPE | SUPPORTS THESE<br>MEMORY DEVICES                  | TOP 28 PIN<br>SOCKET WIRING<br>VERSION |

|---------|--------------------|--------------------|---------------------------------------------------|----------------------------------------|

| MK97400 | Ĕ                  | Ę                  | 2716, 2516, 2532, 2758<br>MK34000 ROM             | 4                                      |

| MK97410 | Open<br>Drain      | Open               | 2716, 2516, 2532, 2758<br>MK34000 ROM             | 4                                      |

| MK97500 | Ę                  | Open               | 2716, 2516, 2532, 2758<br>MK34000 ROM             | 80                                     |

| MK97501 | É                  | Open               | 2764, 2732, MK37000 ROM<br>MK34000 ROM            | U                                      |

| MK97503 | Ę                  | Open               | Use connector from<br>28 pin socket to memory bus | Q                                      |

found the ST instruction useful even in devices like the 3870/20 which have no executable RAM. In this case it causes the data counter to increment (to perhaps totalize some event) but otherwise does nothing as one cannot write the internal ROM. No internal conflicts will occur if one attempts to write a 3870 ROM location. Most 97500 versions place a RD (read, active low) signal on the top socketp in which matches the OE (output enable, active low) input on most memories. Since RD will remain high druin an operand write, the external memory would not have its data outputs enabled and no conflict will occur.

#### MREQ (97500 Series Only)

This is an active low output which occurs during each machine cycle. It goes high at the start of each cycle then goes low for the remainder of the cycle.

#### RD (97500 Series Only)

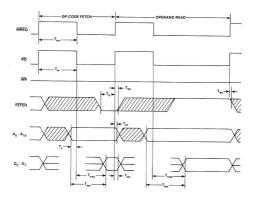

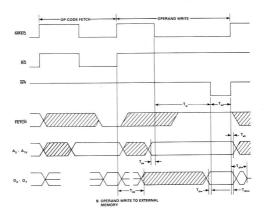

97400 SERIES TIMING Read Cycle Figure 8

This is the active low read output which goes high at the start of each cycle then goes low if data (op-codes or operands) are to be read from external memory. During cycles wherein a strictly internal operation occurs, RD will

remain high. It will also remain high during an operand write cycle.

#### WR (97500 Series Only)

This is the active low write control output. It is normally high but will go low then return high during an operand write if the address is not that of internal executable RAM.

#### FETCH (97500 Series Only)

This is the active low fetch status signal which signals that an op-code fetch occurred during that cycle. It is generated for use of the 97500 as a development system component.

It will go low during all op-code fetches whether from internal or external memory.

#### 38P70 EXTERNAL MEMORY TIMING

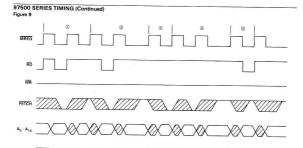

The following Figures show the relative waveforms for the signals used to interface with external memory. The timing parameters are labeled. Their values are given in the A.C. Characteristics section of the Electrical Specifications.

A. OP-CODE AND OPERAND READ FROM EXTERNAL MEMORY

#### C. EXAMPLES OF VARIOUS CYCLES

- Op-code fetch from external memory followed by an internal cycle (short cycle).

- Op-code fetch from external memory followed by an internal cycle (long cycle) such as an operand read or write internal executable RAM.

- ① Op-code fetch from internal executable RAM.

① Op-code fetch from internal executable RAM followed by a internal cycle (long cycle) such as an operand read or write of internal executable RAM.

- (5) First cycle of an interrupt acknowledge. Had an interrupt not occurred, this would have been an op-code fetch. If it would have been an external op-code fetch, RD will still go low but FETCH will not indicate a fetch cycle. Externally this would appear to be an operand read except that it occurs in a short cycle and all real operand read except that

#### 3870 TIME BASE OPTIONS

The 3870 contains an on-chip oscillator circuit which provides an internal clock. The frequency of the oscillator circuit is set from the external time base network. The time base for the 3870 may originate from one of four sources:

- 1) Crystal

- 2) LC Network

- 3) RC Network

- 4) External Clock

The type of network which is to be used with the mask ROM MK3870 must be specified at the time when mask ROM devices are ordered. However, the MK38P70 may operate with any of the four configurations so that it may emulate any configuration used with a mask ROM device.

The specifications for the four configurations are given in the following text. There is an internal 26 pf capacitor between XTL 1 and GND and an internal 26 pf capacitor between XTL 2 and GND. Thus, external capacitors are not necessarily required. In all external clock modes the external time base frequently is divided by two to form the internal PHI clock.

#### CRYSTAL SELECTION

The use of a crystal as the time base is highly recommended as the frequency stability and reproduction from system to system is unsurpassed. The 8870 has an internal divide by two to allow the use of inexpensive and widely available TV toolor Burst Crystals (3.58 MHz), Figure 11 lists the required crystal parameters for use with the 3870. The Crystal Mode time base configuration is shown in Figure 10.

Through careful buffering of the XTL1 pin it may be possible to amplify this wewform and distribute it to other devices. However, Mostek recommends that a separate active device (such as a 4700 series TIL pate) be used to oscillate the crystal and that the waveform from that oscillator be buffered and supplied to all devices; including the 8370, if a single crystal is to provide the time base for more than just a single 3870.

While a ceramic resonator may work with the 3870 crystal oscillator, it was designed specifically to support the use of this component. Thus, Mostek does not support the use of a ceramic resonator either through proper testing, parametric specification, or applications support.

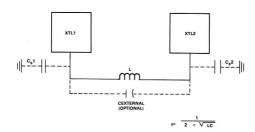

#### LC NETWORK

The LC time base configuration can be used to provide a less expensive time base for the 3870 than can be provided whe a crystal. However, the LC configuration is much less accurate than is the crystal configuration. The LC time configuration is shown in Figure 12. Also shown in the figure are the specified parameters for the LC composition of the compo

#### CRYSTAL MODE CONNECTION

Figure 10

#### CRYSTAL PARAMETERS

Figure 11

- a) Parallel resonance, fundamental mode AT-Cut

- b) Shunt capacitance (Cn) = 7 pf max.

- c) Series resistance (Rs) = See table

- d) Heldes = Con table below

| a) | Holder | - See | table | below. |  |

|----|--------|-------|-------|--------|--|

|    |        |       |       |        |  |

| Frequency     | Series Resistance | Holder |

|---------------|-------------------|--------|

| f = 2-2.7 MHz | Rs = 300 ohms max | HC-6   |

|               |                   | HC-33  |

| f = 2.8-4 MHz | Rs = 150 ohms max | HC-6   |

|               |                   | HC-18* |

|               |                   | HC-25* |

|               |                   | HC-33  |

<sup>\*</sup>This holder may not be available at frequencies near the lower end of this range.

capacitances,  $C_{\rm S}$ , and  $C_{\rm S}$ ,  $C_{\rm TL}$ , is the capacitance looking into the internal low poor network at XTL1 and XTL2  $C_{\rm KL}$  is listed under the "Capacitance" section of the Electrical Specifications.  $C_{\rm S}$ 1 and  $C_{\rm S}2$  are stray capacitances from XTL1 to ground and from XTL2 to ground, respectively. C external should also include the stray shunt capacitance across the inductor. This is typically in the 3 to 5 pf range and significant error can result if it is not included in the frequency calculation.

Variation in time base frequency with the LC network can arise from one of four sources: 1) Variation in the value of the inductor. 2) Variation in the value of the external capacitance of the 3870 at XTL1 and XTL2 and 4) Variation in the amount of stray capacitance which exists in the circuit. Therefore, the actual frequency which is generated by the LC circuit is within a range of possible frequencies, where the range of frequencies is determined by the worst case variation in circuit parameters. The designer must select component values such that the range of possible frequencies with the LC mode does not go outside of the specified operating frequency range for the 3870.

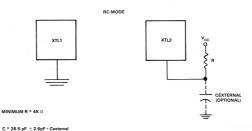

#### RC CLOCK CONFIGURATION

The time base for the 3870 may be provided from an RC network tied to the XTL2 pir, when XTL1 is grounded, aschematic picturing the RC clock configuration is shown in Figure 13. The RC time base configuration is intended to provide an inexpensive time base configuration is intended to myoride an inexpensive time base source for applications in which timing is not critical. Some users have elected to tune each until using a variable resistor or external capacitor, for increased time the search of the s

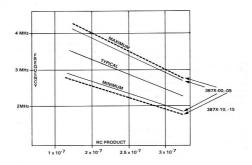

Cystal or LC time base configuration. Figure 14 illustrates a curve which gives the resulting operating frequency a particular RC value. The x-axis represents the product of the value of the resistor times the value of the capacitor. Note that three curves are actually shown. The curve in the middle represents the nominal frequency obtained for a given value of RC. A maximum curve and a minimum curve for different types of 3870 devices are also shown in the diagram.

The designer must select the RC product such that a frequency of less than 2 MHz is not possible, taking into account the maximum possible RC product and using the minimum curve shown in Figure 14 below. Also, the RC product must not allow a frequency of more than 4 MHz, taking into account the minimum possible R and C and using the Maximum curve shown below. Temperature induced variations in the external components should be considered in calculating the RC product.

Frequency variation from unit to unit owing to switching speed and level at constant temperature and V<sub>CC</sub> = + or - 5 percent.

Frequency variation due to V<sub>CC</sub> with all other parameters constant with respect to +5V = +7 percent to -4 percent on all devices.

Frequency variation due to temperature with respect to 25 C (all other parameters constant) is as follows:

VADIATION

| rani #       | VARIATION                 |

|--------------|---------------------------|

| 387X-00, -05 | +6 percent to - 9 percent |

| 387X-10, -15 | +9 percent to -12 percent |

----

FREQUENCY VS. RC

Figure 14

Variations in frequency due to variations in RC components may be calculated as follows:

Maximum RC = (R max) (C external max + C<sub>XTL</sub> max)

Minimum RC = (R min) (C external min + Cyrt min)

Typical RC = (R typ) (C external typ +

{C<sub>XTL</sub> max + C<sub>XTL</sub> min})

Positive Freq. Variation = RC typical - RC minimum RC typical

Negative Freq. Variation = RC maximum - RC typical due to RC Components RC typical

Total frequency variation due to all factors:

387X-00. -05

387X-10. -15

= +18 percent plus positive = +21 percent plus positive frequency variation due frequency variation due

to RC components to RC components =-18 percent minus negative frequency variation due to RC components

= -21 percent minus negative frequency variation due to RC components

Total frequency variation due to V<sub>CC</sub> and temperature of a unit tuned to frequency at +5V V<sub>CC</sub>, 25 C

387X-00, -05 = + 13 percent

387X-10, -15 = + 16 percent

## EXTERNAL CLOCK CONFIGURATION

The connection for the external clock time base configuration is shown in Figure 15. Refer to the DC Characteristics section for proper input levels and current requirements.

Refer to the Capacitance section of the appropriate 3870 Family device data sheet for input capacitance.

#### EXTERNAL MODE CONNECTION

Figure 15